# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.) *G06F 21/70* (2013.01)

(21) 출원번호

10-2014-0066709

(22) 출원일자

2014년06월02일

심사청구일자 2014년06월02일 (65) 공개번호 10-2015-0138611 (43) 공개일자 2015년12월10일

(56) 선행기술조사문헌 KR101393806 B1\* KR1019940012127 A\* JP2945139 B2

\*는 심사관에 의하여 인용된 문헌

기술이전 희망: 기술양도, 실시권허여, 기술지도

(45) 공고일자 2016년02월15일

(11) 등록번호 10-1593166

(24) 등록일자 2016년02월02일

(73) 특허권자

#### 한국전자통신연구원

대전광역시 유성구 가정로 218 (가정동)

(72) 발명자

### 김문석

대전광역시 유성구 유성대로 1559

#### 유상경

대전광역시 유성구 유성대로 1559 (*뒷면에 계속*)

(74) 대리인

한양특허법인

전체 청구항 수 : 총 8 항

심사관 : 구본재

# (54) 발명의 명칭 물리적 복제 방지 함수의 오류를 방지하는 장치 및 그 방법

#### (57) 요 약

본 발명은 SRAM(static random access memory) 기반의 물리적 복제 방지 함수의 비트 오류를 방지하는 장치 및 그 방법에 관한 것이다. 물리적 복제 방지 함수의 오류를 방지하는 방법은 휘발성 메모리 소자를 기반으로 하는 물리적 복제 방지 함수에서 임의의 값을 입력값으로 선택하고, 선택한 입력값에 대응하는 응답을 확인하는 단계, 응답에 해당하는 복수개의 비트를 가지는 셀을 오류 빈도에 따라 구분하는 단계, 구분한 결과 중 오류가 발생하지 않는 화이트 셀의 개수를 계산하는 단계 및 화이트 셀의 개수가 이전에 설정한 화이트 셀의 문턱 개수보다 많은지 확인하고, 확인한 결과를 토대로 물리적 복제 방지 함수의 입력값을 선택하는 단계를 포함한다.

# 대 표 도 - 도3

(72) 발명자

류석

대전광역시 유성구 유성대로 1559

이봉수

대전광역시 유성구 유성대로 1559

이래

대전광역시 유성구 유성대로 1559

강준기

대전광역시 유성구 유성대로 1559

이상한

대전광역시 유성구 유성대로 1559

# 특허청구의 범위

#### 청구항 1

휘발성 메모리 소자를 기반으로 하는 물리적 복제 방지 함수에서 임의의 값을 입력값으로 선택하고, 선택한 입력값에 대응하는 응답을 확인하는 단계;

상기 응답에 해당하는 복수개의 비트를 가지는 셀을 오류 빈도에 따라 구분하는 단계;

구분한 결과 중 오류가 발생하지 않는 화이트 셀의 개수를 계산하는 단계; 및

상기 화이트 셀의 개수가 이전에 설정한 화이트 셀의 문턱 개수보다 많은지 확인하고, 확인한 결과를 토대로 상기 물리적 복제 방지 함수의 입력값을 선택하는 단계

를 포함하고,

상기 구분하는 단계는

상기 셀에 전원을 차단/인가 후 셀의 논리 값의 변화를 토대로 오류 빈도를 확인하고, 확인한 결과를 토대로 셀을 구분하는 것을 특징으로 하는 물리적 복제 방지 함수의 오류를 방지하는 방법.

# 청구항 2

청구항 1에 있어서.

상기 확인하는 단계는

상기 휘발성 메모리 소자의 메모리 주소에 해당하는 임의의 값을 입력값으로 선택하고, 상기 메모리 주소의 데 이터를 응답으로 확인하는 것을 특징으로 하는 물리적 복제 방지 함수의 오류를 방지하는 방법.

# 청구항 3

청구항 1에 있어서,

상기 확인하는 단계는

난수 발생 또는 다른 물리적 복제 방지 함수의 응답을 통해 획득할 수 있는 임의의 값을 상기 입력값으로 선택하는 것을 특징으로 하는 물리적 복제 방지 함수의 오류를 방지하는 방법.

## 청구항 4

삭제

#### 청구항 5

청구항 1에 있어서,

상기 구분하는 단계는

오류가 발생하지 않는 화이트 셀, 오류가 지속적으로 발생하는 블랙 셀, 상기 화이트 셀과 상기 블랙 셀의 중간 오류 빈도를 가지는 그레이 셀로 구분하는 것을 특징으로 하는 물리적 복제 방지 함수의 오류를 방지하는 방법.

# 청구항 6

휘발성 메모리 소자를 기반으로 하는 물리적 복제 방지 함수에서 임의의 값을 입력값으로 선택하고, 선택한 입력값에 대응하는 응답을 확인하는 확인부;

상기 응답에 해당하는 복수개의 비트를 가지는 셀을 오류 빈도에 따라 구분하는 셀 구분부;

구분한 결과 중 오류가 발생하지 않는 화이트 셀의 개수를 계산하는 계산부; 및

상기 화이트 셀의 개수가 이전에 설정한 화이트 셀의 문턱 개수보다 많은지 확인하고, 확인한 결과를 토대로 상기 물리적 복제 방지 함수의 입력값을 선택하는 선택부

를 포함하고,

상기 셀 구분부는

상기 셀에 전원을 차단/인가 후 셀의 논리 값의 변화를 토대로 오류 빈도를 확인하고, 확인한 결과를 토대로 셀을 구분하는 것을 특징으로 하는 물리적 복제 방지 함수의 오류를 방지하는 장치.

#### 청구항 7

청구항 6에 있어서,

상기 확인부는

상기 휘발성 메모리 소자의 메모리 주소에 해당하는 임의의 값을 입력값으로 선택하고, 상기 메모리 주소의 데 이터를 응답으로 확인하는 것을 특징으로 하는 물리적 복제 방지 함수의 오류를 방지하는 장치.

### 청구항 8

청구항 6에 있어서.

상기 확인부는

난수 발생 또는 다른 물리적 복제 방지 함수의 응답을 통해 획득할 수 있는 임의의 값을 상기 입력값으로 선택하는 것을 특징으로 하는 물리적 복제 방지 함수의 오류를 방지하는 장치.

# 청구항 9

삭제

#### 청구항 10

청구항 6에 있어서,

상기 셀 구분부는

오류가 발생하지 않는 화이트 셀, 오류가 지속적으로 발생하는 블랙 셀, 상기 화이트 셀과 상기 블랙 셀의 중간 오류 빈도를 가지는 그레이 셀로 구분하는 것을 특징으로 하는 물리적 복제 방지 함수의 오류를 방지하는 장치.

# 명세서

[0001]

#### 기 술 분 야

본 발명은 물리적 복제 방지 함수의 오류를 방지하는 장치 및 그 방법에 관한 것으로, 특히 SRAM(static random access memory) 기반의 물리적 복제 방지 함수의 비트 오류를 방지하는 장치 및 그 방법에 관한 것이다.

# 배경기술

- [0002] 동일한 반도체 공정 조건으로 공정을 하여도 예측 불가능하게 소자마다 물리적 또는 전기적 파라미터의 변화가 생긴다.

- [0003] 물리적 복제 방지 함수(Physically unclonable function, 이하 "PUF"라고도 함)는 예측 불가능한 결과를 만들어내는 소자에 적용할 수 있다. 이와 같이 물리적 복제 방지 함수가 적용된 소자 즉, PUF는 한국공개특허 제10-2014-00059485호 "PUF를 이용한 기기 인증 장치 및 방법"과 같이, 기기 인증 기능, 위조 방지 기능 등으로 사용가능하다.

- [0004] 최근, PUF 중에서 예측 불가능성, 엔트로피 측면에서 우수한 특성을 갖는 SRAM 기반의 PUF가 많은 주목을 받고 있다. 그러나, SRAM 기반의 PUF 경우에도 견고성이 완벽하지 않은 단점이 있다. 이러한 문제를 해결하기 위해 오류정정부호화 PUF를 연결하여 견고성을 높여왔다.

- [0005] SRAM PUF의 경우에는 6% 내외의 비트 에러율을 가져서 오류 정정율이 높은 오류정정부호를 사용해야한다. 또한, 오류 정정율이 높은 오류정정부호는 하드웨어/소프트웨어 어떤 쪽으로 구현하더라도 큰 오버헤드를 가진다.

- [0006] 따라서, SRAM 기반의 PUF의 비트 오류를 방지하는 기술이 필요하다.

# 발명의 내용

#### 해결하려는 과제

[0007] 본 발명의 목적은 SRAM(static random access memory) 기반의 물리적 복제 방지 함수의 비트 오류를 방지하는 장치 및 그 방법을 제공하는 것이다.

# 과제의 해결 수단

- [0008] 상기한 목적을 달성하기 위한 본 발명에 따른 물리적 복제 방지 함수의 오류를 방지하는 방법은

- [0009] 휘발성 메모리 소자를 기반으로 하는 물리적 복제 방지 함수에서 임의의 값을 입력값으로 선택하고, 선택한 입력값에 대응하는 응답을 확인하는 단계; 상기 응답에 해당하는 복수개의 비트를 가지는 셀을 오류 빈도에 따라 구분하는 단계; 구분한 결과 중 오류가 발생하지 않는 화이트 셀의 개수를 계산하는 단계; 및 상기 화이트 셀의 개수가 이전에 설정한 화이트 셀의 문턱 개수보다 많은지 확인하고, 확인한 결과를 토대로 상기 물리적 복제 방지 함수의 입력값을 선택하는 단계를 포함한다.

- [0010] 이 때, 상기 확인하는 단계는 상기 휘발성 메모리 소자의 메모리 주소에 해당하는 임의의 값을 입력값으로 선택하고, 상기 메모리 주소의 데이터를 응답으로 확인하는 것을 특징으로 한다.

- [0011] 이 때, 상기 확인하는 단계는 난수 발생 또는 다른 물리적 복제 방지 함수의 응답을 통해 획득할 수 있는 임의 의 값을 상기 입력값으로 선택하는 것을 특징으로 한다.

- [0012] 이 때, 상기 구분하는 단계는 상기 셀에 전원을 차단/인가 후 셀의 논리 값의 변화를 토대로 오류 빈도를 확인하고, 확인한 결과를 토대로 셀을 구분하는 것을 특징으로 한다.

- [0013] 이 때, 상기 구분하는 단계는 오류가 발생하지 않는 화이트 셀, 오류가 지속적으로 발생하는 블랙 셀, 상기 화이트 셀과 상기 블랙 셀의 중간 오류 빈도를 가지는 그레이 셀로 구분하는 것을 특징으로 한다.

- [0014] 또한, 본 발명의 일실시예에 따른 물리적 복제 방지 함수의 오류를 방지하는 장치는

- [0015] 휘발성 메모리 소자를 기반으로 하는 물리적 복제 방지 함수에서 임의의 값을 입력값으로 선택하고, 선택한 입력값에 대응하는 응답을 확인하는 확인부; 상기 응답에 해당하는 복수개의 비트를 가지는 셀을 오류 빈도에 따라 구분하는 셀 구분부; 구분한 결과 중 오류가 발생하지 않는 화이트 셀의 개수를 계산하는 계산부; 및 상기화이트 셀의 개수가 이전에 설정한 화이트 셀의 문턱 개수보다 많은지 확인하고, 확인한 결과를 토대로 상기 물리적 복제 방지 함수의 입력값을 선택하는 선택부를 포함한다.

- [0016] 이 때, 상기 확인부는 상기 휘발성 메모리 소자의 메모리 주소에 해당하는 임의의 값을 입력값으로 선택하고, 상기 메모리 주소의 데이터를 응답으로 확인하는 것을 특징으로 한다.

- [0017] 이 때, 상기 확인부는 난수 발생 또는 다른 물리적 복제 방지 함수의 응답을 통해 획득할 수 있는 임의의 값을 상기 입력값으로 선택하는 것을 특징으로 한다.

- [0018] 이 때, 상기 구분부는 상기 셀에 전원을 차단/인가 후 셀의 논리 값의 변화를 토대로 오류 빈도를 확인하고, 확 인한 결과를 토대로 셀을 구분하는 것을 특징으로 한다.

- [0019] 이 때, 상기 구분부는 오류가 발생하지 않는 화이트 셀, 오류가 지속적으로 발생하는 블랙 셀, 상기 화이트 셀과 상기 블랙 셀의 중간 오류 빈도를 가지는 그레이 셀로 구분하는 것을 특징으로 한다.

### 발명의 효과

- [0020] 본 발명은 SRAM(static random access memory) 기반의 물리적 복제 방지 함수의 비트 오류를 방지하는 과정을 통해 6% 내외의 비트에러율이 0%로 수렴하게 될 수 있도록 한다.

- [0021] 또한, 본 발명은 미리 설정한 화이트 셀의 문턱 개수를 조절함으로써, PUF 사용 목적에 따른 PUF의 오류율도 조절할 수 있다. 따라서, 본 발명은 오류정정부호 없이도 견고성이 높은 SRAM 기반의 PUF를 구현할 수 있다.

#### 도면의 간단한 설명

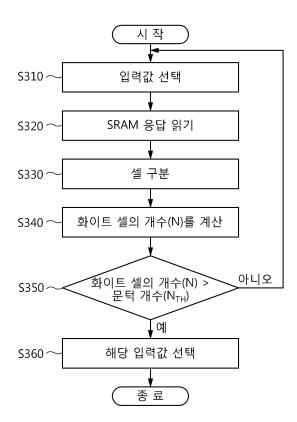

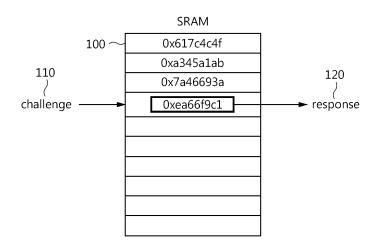

[0022] 도 1은 본 발명의 실시예에 따른 SRAM 기반의 물리적 복제 방지 함수의 입력 및 출력을 나타내는 도면이다.

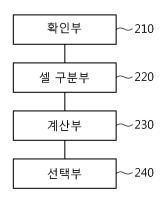

도 2는 본 발명의 실시예에 따른 물리적 복제 방지 함수의 오류를 방지하는 장치를 개략적으로 나타내는 구성도이다.

도 3은 본 발명의 실시예에 따른 물리적 복제 방지 함수의 오류를 방지하는 방법을 나타내는 흐름도이다.

# 발명을 실시하기 위한 구체적인 내용

- [0023] 본 발명을 첨부된 도면을 참조하여 상세히 설명하면 다음과 같다. 여기서, 반복되는 설명, 본 발명의 요지를 불필요하게 흐릴 수 있는 공지 기능, 및 구성에 대한 상세한 설명은 생략한다. 본 발명의 실시형태는 당 업계에서 평균적인 지식을 가진 자에게 본 발명을 보다 완전하게 설명하기 위해서 제공되는 것이다. 따라서, 도면에서의 요소들의 형상 및 크기 등은 보다 명확한 설명을 위해 과장될 수 있다.

- [0024] 이하, 본 발명에 따른 바람직한 실시예 따른 SRAM(static random access memory) 기반의 물리적 복제 방지 함수의 오류를 방지하는 장치 및 그 방법에 대하여 첨부한 도면을 참조하여 상세하게 설명한다.

- [0025] 도 1은 본 발명의 실시예에 따른 SRAM 기반의 물리적 복제 방지 함수의 입력 및 출력을 나타내는 도면이다.

- [0026] 도 1을 참고하면, SRAM(100)은 빠른 읽기/쓰기 속도로 데이터를 저장하는 휘발성 메모리 소자이다.

- [0027] 일반적으로, SRAM(100)의 전원을 일정 시간 차단한 후 전원을 인가하고, SRAM(100)을 초기화하지 않을 경우 예측 불가능한 데이터를 읽어 올 수 있다. 이 데이터 값은 물리적 복제 방지 함수(physically unclonable function, 이하 "PUF"라고도 함)에 적용할 수 있다.

- [0028] SRAM(100) 기반의 PUF는 예를 들어, 메모리 주소를 입력값(challenge)(110)으로 하는 경우, 메모리 주소의 데이 터를 응답(response)(120)으로 출력한다. 여기서, SRAM(100) 기반의 PUF의 견고성은 동일한 입력값(110)의 응답(120)이 전원 차단/인가 후에도 동일한 응답으로 출력되는 것을 의미한다.

- [0029] SRAM 기반의 PUF의 견고성은 완벽하지 않고 6% 내외의 비트 에러율을 보인다. 이때, SRAM 하드웨어 셀에서 비트 에러가 발생한다. SRAM 기반의 PUF의 에러는 전체 셀 중 4%의 셀들이 지속적으로 오류를 발생시킨다.

- [0030] 본 발명의 실시예에 따른 물리적 복제 방지 함수의 오류를 방지하는 장치는 SRAM 셀의 오류 발생빈도 여부를 기준으로 SRAM 셀을 구분할 수 있다. 여기서, SRAM 셀은 화이트(WHITE) 셀, 그레이(GRAY) 셀, 블랙(BLACK) 셀로 구분할 수 있다.

- [0031] 화이트 셀은 오류가 발생하지 않는 셀, 블랙 셀은 오류가 지속적으로 발생하는 셀, 그레이 셀은 화이트 셀과 블랙 셀의 중간 정도의 오류 빈도를 가지는 셀이다. 여기서, 본 발명의 실시예에 따른 화이트 셀, 그레이 셀 및 블랙 셀의 분포는 연집 형태를 가지지 않고, 무작위 형태를 가지는 것을 특징으로 하며, 이에 한정되지 않는다.

- [0032] 다음, 물리적 복제 방지 함수의 오류를 방지하는 장치를 도 2를 참조하여 상세하게 설명한다.

- [0033] 도 2는 본 발명의 실시예에 따른 물리적 복제 방지 함수의 오류를 방지하는 장치를 개략적으로 나타내는 구성도 이다.

- [0034] 먼저, 본 발명의 실시예에 따른 물리적 복제 방지 함수의 오류를 방지하는 장치(200)는 SRAM PUF 셀들의 오류분 포가 특정 셀에만 집중되고 이 분포가 무작위 특성을 보이는 경우에 오류를 방지하는 것을 특징으로 하며, 이에 한정되지 않는다.

- [0035] 또한, SRAM(100) 기반의 물리적 복제 방지 함수(PUF)는 예를 들어, 메모리 주소를 입력값(challenge)(110)으로 하는 경우, 메모리 주소의 데이터를 응답(response)(120)으로 출력한다. 여기서, 메모리 주소는 1워드(32 비트)의 데이터를 가지고 있다. 즉, SRAM(100)에서 입력값은 32 비트의 응답을 가지고 있다고 가정할 수 있으며, 이에 한정되지 않는다.

- [0036] 도 2를 참고하면, 물리적 복제 방지 함수의 오류를 방지하는 장치(200)는 확인부(210), 셀 구분부(220), 계산부 (230) 및 선택부(240)를 포함한다.

- [0037] 확인부(210)는 임의의 값을 입력값으로 선택하고, 이에 해당하는 SRAM 응답을 확인한다. 여기서, 임의의 값은 난수 발생 또는 다른 PUF의 응답 등을 통해 획득할 수 있는 임의의 값에 해당한다.

- [0038] 셀 구분부(220)는 확인부(210)에서 확인한 결과 즉, 32 비트의 셀을 오류 빈도에 대응하게 화이트 셀, 그레이 셀, 블랙 셀로 구분한다.

- [0039] 구체적으로, 셀 구분부(220)는 SRAM 셀에 전원을 차단/인가 후 셀들의 논리 값의 변화를 토대로 오류 빈도를 확인하고, 이를 통해 셀을 구분한다.

- [0040] 예를 들어, 해당 셀이 18번의 전원 차단/인가 후 SRAM 응답이 "1"이 9번, "0"이 9번으로 확인 되는 경우에는 해당 셀을 블랙 셀로 구분한다. 반면에, 해당 셀이 18번의 전원 차단/인가 후 SRAM 응답이 "1" 또는 "0"이 18번으로 확인 되는 경우에는 해당 셀을 화이트 셀로 구분한다.

- [0041] 계산부(230)는 셀 구분부(220)에서 셀을 구분한 후에, 해당 SPRM 셀 중 화이트 셀의 개수(N)를 계산한다.

- [0042] 선택부(240)는 계산부(230)에서 계산한 화이트 셀의 개수(N)가 이전에 설정한 화이트 셀의 문턱 개수(N<sub>H</sub>) 보다 많은지를 확인하고, 확인한 결과를 토대로 해당 입력값 즉, 물리적 복제 방지 함수의 입력값을 선택한다.

- [0043] 구체적으로, 선택부(240)는 계산부(230)에서 계산한 화이트 셀의 개수(N)가 화이트 셀의 문턱 개수(N<sub>TH</sub>)보다 많은 경우, 해당 입력값을 양호 입력(good challenge)으로 간주하고 해당 입력값을 선택한다. 이때, 화이트 셀의 문턱 개수(N<sub>TH</sub>)의 설정에 따른 트레이드 오프가 존재 할 수 있다. 화이트 셀의 문턱 개수(N<sub>TH</sub>)가 클수록 오류발생 확률은 감소하지만, 조건을 만족하는 해당 입력값의 개수가 줄어들어서 SRAM의 더 많은 데이터가 필요하다. 반면에, 화이트 셀의 문턱 개수(N<sub>TH</sub>)가 작아질수록 조건을 만족하는 해당 입력값의 개수는 증가하지만, 오류발생 확률은 높아진다.

- [0044] 이와 같이, 본 발명의 실시예에 따른 물리적 복제 방지 함수의 오류를 방지하는 장치는 SRAM 전체 셀 중 오류가 발생하지 않는 입력값을 찾는 절차와 동일할 수 있으며 이에 한정되지 않는다. 예를 들어, 본 발명은 1024비트의 SRAM 기반의 PUF에서 데이터가 필요한 경우에, 32개의 양호 입력값을 선택하여, 오류가 발생하지 않는 SRAM 기반의 물리적 복제 방지 함수를 운용할 수 있다.

- [0045] 다음, 물리적 복제 방지 함수의 오류를 방지하는 방법을 도 3을 참조하여 상세하게 설명한다.

- [0046] 도 3은 본 발명의 실시예에 따른 물리적 복제 방지 함수의 오류를 방지하는 방법을 나타내는 흐름도이다.

- [0047] 도 3을 참고하면, 물리적 복제 방지 함수의 오류를 방지하는 장치는 임의의 값을 입력값으로 선택한다(S310). 여기서, 임의의 값은 난수 발생 또는 다른 PUF의 응답 등을 통해 획득할 수 있는 임의의 값에 해당한다.

- [0048] 물리적 복제 방지 함수의 오류를 방지하는 장치는 S310 단계에서 선택한 입력값에 해당하는 SRAM 응답을 확인한다(S320).

- [0049] 물리적 복제 방지 함수의 오류를 방지하는 장치는 SRAM 응답에 대응하는 32비트의 셀을 오류 빈도에 대응하게 화이트 셀, 그레이 셀, 블랙 셀로 구분한다(S330).

- [0050] 구체적으로, 물리적 복제 방지 함수의 오류를 방지하는 장치는 SRAM 셀에 전원을 차단/인가 후 셀들의 논리 값의 변화를 토대로 오류 빈도를 확인하고, 이를 통해 셀을 구분한다. 여기서, SRAM 셀은 화이트(WHITE) 셀, 그레이(GRAY) 셀, 블랙(BLACK) 셀로 구분할 수 있다.

- [0051] 화이트 셀은 오류가 발생하지 않는 셀, 블랙 셀은 오류가 지속적으로 발생하는 셀, 그레이 셀은 화이트 셀과 블랙 셀의 중간 정도의 오류 빈도를 가지는 셀이다. 여기서, 본 발명의 실시예에 따른 화이트 셀, 그레이 셀 및 블랙 셀의 분포는 연집 형태를 가지지 않고, 무작위 형태를 가지는 것을 특징으로 하며, 이에 한정되지 않는다.

- [0052] 물리적 복제 방지 함수의 오류를 방지하는 장치는 S330 단계에서 구분한 후에, 해당 SPRM 셀 중 화이트 셀의 개수(N)를 계산한다(S340).

- [0053] 물리적 복제 방지 함수의 오류를 방지하는 장치는 S340 단계에서 계산한 화이트 셀의 개수(N)가 이전에 설정한 화이트 셀의 문턱 개수(N<sub>TH</sub>) 보다 많은지를 확인하고, 확인한 결과를 토대로 해당 입력값을 선택한다(S350).

- [0054] 물리적 복제 방지 함수의 오류를 방지하는 장치는 S340 단계에서 계산한 화이트 셀의 개수(N)가 화이트 셀의 문턱 개수(N<sub>TH</sub>)보다 많은 경우, 해당 입력값을 양호 입력(good challenge)으로 간주하고 해당 입력값을 선택한다. 이때, 화이트 셀의 문턱 개수(N<sub>TH</sub>)의 설정에 따른 트레이드 오프가 존재 할 수 있다. 화이트 셀의 문턱 개수 (N<sub>TH</sub>)가 클수록 오류발생 확률은 감소하지만, 조건을 만족하는 해당 입력값의 개수가 줄어들어서 SRAM의 더 많은 데이터가 필요하다. 반면에, 화이트 셀의 문턱 개수(N<sub>TH</sub>)가 작아질수록 조건을 만족하는 해당 입력값의 개수는 증가하지만, 오류발생 확률은 높아진다.

[0055]

이와 같이, 본 발명은 미리 설정한 화이트 셀의 문턱 개수를 조절함으로써, PUF 사용 목적에 따른 PUF의 오류율도 조절할 수 있다. 따라서, 본 발명은 오류정정부호 없이도 견고성이 높은 SRAM 기반의 PUF를 구현할 수 있다.

[0056]

이상에서와 같이 도면과 명세서에서 최적의 실시예가 개시되었다. 여기서 특정한 용어들이 사용되었으나, 이는 단지 본 발명을 설명하기 위한 목적에서 사용된 것이지 의미 한정이나 특허청구범위에 기재된 본 발명의 범위를 제한하기 위하여 사용된 것은 아니다. 그러므로, 본 기술 분야의 통상의 지식을 가진자라면 이로부터 다양한 변 형 및 균등한 타 실시예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호범위는 첨부 된 특허청구범위의 기술적 사상에 의해 정해져야 할 것이다.

# 부호의 설명

[0057] 10

100; SRAM

110; 입력값 120; 응답

200; 물리적 복제 방지 함수의 오류를 방지하는 장치

210; 확인부 220; 셀 구분부

230; 계산부 240; 선택부

# 도면

# 도면1

# 도면2

# 200

# 도면3